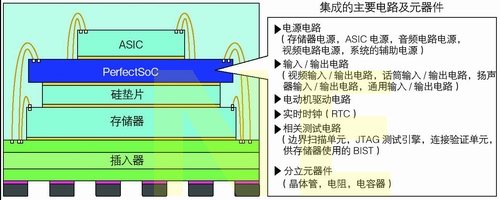

日本TAG(Technology Alliance Group)开发出高密度模块技术SoC" style="color:blue;text-decoration:none;font-weight:normal;">PerfectSoC,可用于实现便携设备的小型化(见图1)。PerfectSoC技术能够将设备电路板上安装的许多元器件集成在单一的电路封装中,这些被集成的元器件包括逻辑电路和存储器、电源等模拟集成电路以及分立元器件。

图1 将ASIC和存储器以外的电路及元器件全部集成在一块芯片上

这种技术可以把电路板上安装的100~200个电子元器件集成到一个封装中,减少元器件的封装面积达80%以上,适用于开发新型的数码相机产品。由于这种技术能够降低成本并缩短开发周期,因此,目前已有多家数码相机厂商正在考虑采用。据估计,在2008年5月~6月间,采用PerfectSoC的数码相机有希望进入实际应用。

极高的集成度

PerfectSoC可以有效提高封装密度的原因是,它继承了以前的SiP(系统级封装)及SoC(片上系统)的优点,同时,又采用了能消除两者缺点的结构。

现有的SiP的优势在于能够将复合存储器等数字电路重叠许多层,SoC的优势则是把制造工序类似的多个电路集成在一块芯片上,从而将制造成本降到最低。但是,在采用了SiP或SoC的许多设备中,电路板上仍然会有许多模拟芯片及分立元器件。这是因为,过去的SiP或SoC的结构不适于集成模拟电路及分立元器件。

而PerfectSoC将上述各种模拟电路和分立元器件以及测试电路等都集成在同一块芯片中,并且采用叠层的方法将这块芯片和半导体厂商提供的ASIC或存储器等放在同一个封装里。可以说,PerfectSoC兼具SiP和SoC两者的优点。在以前的SiP中,不少产品内置有用于集成电路内部工作测试的边界扫描单元(BSC)。在PerfectSoC中也能内置BSC,各电路的测试将变得非常容易。

为了将电源等模拟电路及分立元器件等集成在一块芯片上,PerfectSoC中特意利用了0.5mm或0.35mm等成熟的CMOS工艺。因为使用了成熟的制造工艺,因此很容易确保电源电路所需要的高达7V的耐压,并且可以降低生产成本。

据介绍,PerfectSoC从确定技术规格到批量生产所需要的时间很短,只有半年左右。因为作为基础的IP核可以事先准备好,当接到实际订单时,根据顾客的要求更换电路及元器件的组合形式等就可以了。

[NIKKEI ELECTRONICS 2007. Nikkei Business Publications, Inc. All rights reserved.] (林咏 译)

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。