2007年秋,在PC及服务器中占主流地位的x86处理器终于进入了4核时代。

AMD公司的4核处理器在2007年9月上市,英特尔公司也预定在2007年内推出单芯片封装的4核产品。两家公司都明确表示未来将会提供集成8个CPU内核的处理器产品。但是,多核化只不过掀开了处理器内部架构变革的序幕,各厂商正在摸索新的道路。

在半导体行业中,很早就有这样的说法:“不断集成更多CPU内核的多核架构,并不能使处理器的性能像期待的那样得到提高。”但是,在AMD和英特尔公司转向多核架构的2004年,除了依赖这种手段以外再没有其它出路。

多核化是无奈之举

以前,半导体工艺的发展可以带来“一举三得”的效果,包括提高晶体管速度、降低功耗和缩小芯片面积。但是,当制造工艺发展到90nm或65nm时,泄漏电流的问题凸显,沿用以往的内部架构来提高频率的方法难以奏效。为了在不提高工作频率的条件下实现性能的提升,只能增加CPU内核的数量。

在有许多客户机要求进行并行处理的服务器中,多核架构容易获得比较好的效果。但是,问题发生在根据用户的要求运行应用软件的客户机里。由于可能同时运行的软件数量有限,即使可以将各个软件分割以后并行执行,但软件中必须串行执行的部分仍然会妨碍处理性能的提升。许多相关人士认为,在目前这种架构的PC中,4~8个内核可能是多核处理器能够获得较好性能提升效果的极限。

集成多个不同类型的内核

另一方面,提供新体验的高级用户接口、动态及静态图像分析等新的应用软件的不断出现,对处理器的处理性能提出了更高的要求。如果处理器仅在目前以CPU内核为主的架构上继续发展,这些新应用可能将无法实现。

2007年9月,英特尔公司董事会名誉主席Gordon Moore在英特尔秋季技术峰会上表示:“众所周知,摩尔定律在物理上是有极限的。大约10年或15年以后,摩尔定律将会遇到根本性障碍,而退出历史舞台。”反过来说,Moore认为,半导体工艺的发展很可能还会像以前那样再延续10年左右。在把工艺发展当作技术推动力的同时,为了越过横亘在多核架构前面的壁垒,处理器应该采用什么样的内部架构呢?

业界想到的方案是采用异构处理器架构,即将不同类型的内核集成在一起。在这种架构中,CPU内核所不擅长的浮点运算及信号处理工作,将由集成在同一块芯片上的其它可编程内核执行。相关人士认为,集成多个不同类型内核的异构多核架构将成为今后处理器的主流架构。

从同构到异构通用处理器将实现SoC化

图形芯片生产商Nvidia公司的总裁兼CEO Jen-Hsun Huang指出:“目前,图形芯片具有的浮点运算性能已经大大超越了处理器。如果能够灵活运用,随着图形芯片的发展,将会涌现出各种各样新的应用。”在占据PC及服务器主流地位的x86处理器中,围绕GPU(图形处理单元)展开的相关研发工作突然活跃起来。

GPU的集成和通用化取得进展

围绕GPU的研发方向主要有两个。首先,是将GPU内核集成到处理器芯片上。AMD公司在2006年7月收购了加拿大的GPU生产商ATI科技公司,并提出了将ATI公司的GPU内核集成到处理器上的Fusion处理器方案。另外,英特尔公司在2007年4月明确表示,正在开发矢量处理器Larrabee(开发代号),其中集成了许多专用于浮点运算的CPU内核。

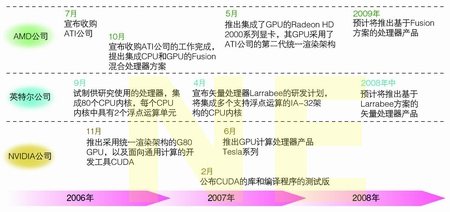

另一个研发方向是,利用GPU擅长对浮点运算进行并行处理的特点,将其用作矢量处理器。这就是面向通用计算领域的GPGPU(General Purpose Computing on GPU),NVIDIA公司从2006年下半年已陆续推出相关的硬件产品及软件开发工具(见图1)。

图1 围绕矢量处理器展开的研发活动

利用多核化暂时回避危机

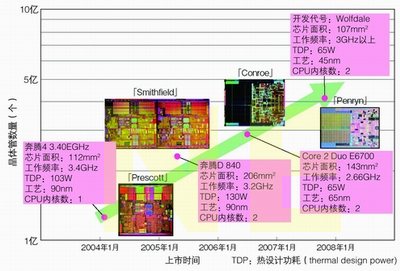

以前,处理器厂商主要依靠采用更先进的工艺来提高处理器的处理性能,但现在,他们遇到了难以逾越的障碍——功耗在不断增大。通过采用更先进的工艺,他们可以缩小晶体管的体积而提高开关速度,并不断提升芯片的工作频率,但这会使功耗超出设备允许的范围。于是就出现了多核解决方案,即利用新工艺的高集成度优势,将多个CPU内核集成在一块芯片上。2004年春,英特尔和AMD公司相继中止了单核产品的开发工作,转向开发集成多个CPU内核的多核产品(见图2)。

图2 利用新工艺增加CPU内核的数量而不是提高频率

目前市场上销售的PC处理器或服务器处理器大多集成有2个以上的CPU内核,4核架构也已经上市。2007年9月,AMD公司的4核Opteron服务器处理器(开发代号为Barcelona)上市。在PC市场,英特尔公司的4核Penryn(开发代号)PC处理器和AMD公司的4核Phenom PC处理器都在2007年11月相继上市。而且,这两家公司均表示计划在2008年~2009年提供8核产品。这些产品都采用同构处理器架构,处理器中集成的是同类型的CPU内核。

同构处理器出现极限

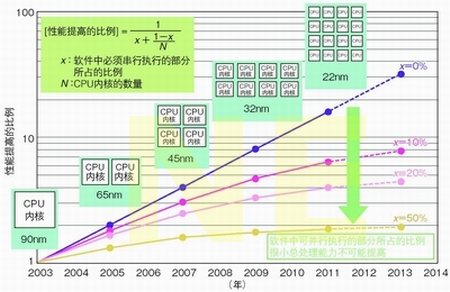

但是,以前就有人指出,通过增加CPU内核来提升处理器的性能,存在一定的极限。达到极限值之后,性能就无法再随着内核数量的增加而提升了。这就是著名的Amdahl定律:即使能够不断增加同类型的CPU内核以加强并行处理能力,但整个系统的处理性能仍然会受到软件中必须串行执行的那部分的制约。

比如,工艺从90nm发展到22nm时,一块芯片中集成的晶体管大约能增加到16倍。但是,当利用这些晶体管将芯片中集成的CPU内核由1个增加到16个时,芯片的整体处理能力却不会简单地提高到16倍。根据Amdahl定律,当软件中必须串行执行的部分占到20%时,整体处理能力只能提高4倍(见图3)。这只是简化计算后得到的结果,还没有考虑用于保持高速缓存相关性时的同步时间,以及多个内核集中访问内存时的待机时间等。如果将实际工作时存在的这些等待时间都考虑在内,整体处理能力的提升很可能还不到原来的4倍。

图3 Amdahl定律

在像服务器那样同时产生多个处理请求,且各处理所涉及的数据都相互独立的应用中,必须串行执行的软件部分很少,针对这类应用的处理器就可以通过集成更多的同类型内核来提高处理性能。Sun微系统公司的UltraSparc T2已经上市,这种服务器处理器集成有8个CPU内核,每个内核包含8个线程,即拥有64线程的并行处理能力。

但是,PC那样的客户机是以执行一个用户的处理请求为主,需要同时启动的应用软件数量很少。而且,即使想要将应用软件变为并行处理,也很难把处理过程中相互独立的部分抽取出来。面向嵌入式设备的处理器厂商普遍认为:“对于客户机中使用的处理器来说,多核化可能发挥效果的极限是4~8个内核。”多核化只不过是一种暂时回避功耗危机的手段。

采用异构处理器摆脱困境

为了摆脱上述困境,处理器厂商注意到,可以利用GPU来应对同构多核处理器遇到的难题。

最近,在苹果公司的iPhone等产品中可以看到,用户对于提高画面质量的要求日益高涨。各种各样的设备都试图采用新的用户接口,以带给用户简单、顺畅、直接的操作体验。另外,许多游戏软件中常常需要进行实时计算,以实时显示游戏里虚拟空间中物体的坐标。有时,还需要利用现实世界的物理规律计算虚拟空间中的物体运动情况,并将其以接近真实的方式表达出来。为了支持这些新应用,处理器厂商开始考虑要发挥GPU的计算能力。

近几年来,GPU理论上的浮点运算性能已经大大超越了通用处理器。NVIDIA公司的GeForce 8800 GPU浮点运算性能的最大值已经达到500GFLOPS以上,而英特尔公司的Core 2 Duo处理器的浮点运算性能只有50GFLOPS左右。按照每单位功耗的浮点运算性能进行比较,GeForce 8800的浮点运算性能约为Core 2 Duo的5倍。

处理器厂商关注GPU的另一个理由是,NVIDIA公司和已被AMD收购的ATI公司都取消了集成多个专用电路的开发方针,这些专用电路主要用于执行图形处理流水线中的各级处理。这两家公司转向使用集成多个通用运算单元的架构,采用这些通用运算单元来支持流水线的各级处理。于是,除了图形处理以外,这种具有新架构的GPU也能被方便地应用于其他领域。可以说,目前的GPU是优化了浮点运算的矢量处理器。

将这种新的GPU内核与CPU内核集成到一起以后,面向并行处理的应用软件所要求的浮点运算及定点运算将由GPU执行;而CPU内核则致力于执行传统处理器的主要任务,即运行操作系统、执行商务软件中的整数运算等。这样,芯片就可以高效地执行和处理大量独立数据的任务,如:面向多个运动对象的计算;对显示画面进行优化的光线跟踪处理(光线渲染);图像的编/解码处理等。

这样一来,处理器厂商不再需要不停地增加处理器中集成的同类型CPU内核的数量,而可以把重点转移到异构多核处理器架构上,将GPU内核和CPU内核集成在一起。也可以说,x86处理器正在向SoC发展。英国Imagination技术公司CEO Hossein Yassaie表示:“在对功耗及成本要求非常严格的嵌入式设备中,很早以前就开始遵循‘利用正确的内核执行正确的处理’的设计方法。现在,这种方法对于PC那样的通用计算设备也变得越来越重要了。”

CPU和GPU的集成取得进展

最早表示要开发异构多核处理器的是AMD公司。GPU的应用得到扩展后,就有越来越多的数据需要通过CPU内核和GPU内核进行交换,因此,为了拥有更宽的通信路径,方法就是将这两种内核集成在同一块芯片上。

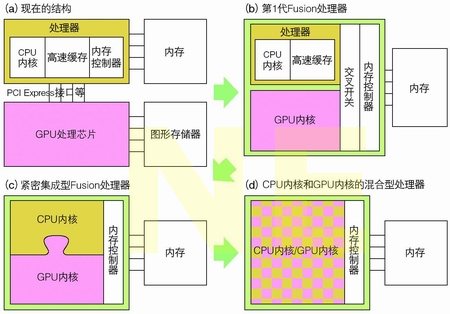

在该公司提出的第一代Fusion方案中,CPU内核和内存之间、GPU内核和内存之间均使用交叉开关进行连接,并且,两种内核通过共享内存进行数据交换。该公司表示,在第一代产品之后,将会加强CPU内核和GPU内核的集成(见图4)。该公司高级副总裁兼CTO Phil Hester表示:“最终目标是制成将CPU内核和GPU内核融合为一体的新型架构。”

图4 AMD公司提出分阶段推进CPU内核和GPU内核的集成方案

异构多核架构中能集成的不只是GPU内核,也可以将进行网络及视频等处理的内核集成到一块芯片上。英特尔公司正在推进Tolapai(开发代号)SoC的开发工作,这种SoC将主要用于各种可联网的嵌入式设备。在这种SoC中,除了支持86指令集的CPU内核之外,还集成有内存控制器、Gb以太网及PCI Express接口电路、用于执行各种编码处理的安全服务单元(Security Service Units)等。英特尔公司所设想的SoC,是将可编程内核或FPGA等和CPU内核集成到一起。这些可编程内核或FPGA就像安全服务单元一样,是专为特定领域内大量存在的运算而特别定制的。该公司计划将Tolapai作为第一批SoC产品推出,然后再依次推出面向各种应用的SoC。

2006年,AMD和英特尔将面向低功耗设备的处理器业务分别出售给了Raza微电子公司和Marvell半导体公司,但这并不意味着这两家公司要退出嵌入式设备市场。这两家公司的新目标是,不仅要将集成了支持86指令集CPU内核的SoC用于PC及服务器,而且还要扩展其应用到数字消费设备以及便携式信息终端等领域。

改变内核数量以适应各种应用

今后,这两家公司将为各种应用提供具有类似内部架构的SoC产品。其中,CPU内核的数量以及GPU内核里用于运算的内核数量等,都可以随要求的运算性能和被允许的功耗做出相应的调整(见图5)。这两家公司的计划是,在便携式设备中使用低功耗CPU内核,在固定式设备或PC等产品中则使用普通CPU内核。预计,在面向PC的SoC中集成的GPU内核,也可能在减少了运算单元的数量之后,集成到面向便携式设备的SoC中。

图5 CPU内核和GPU内核的数量都可以灵活调整

AMD计划在2009年之后的处理器产品系列中分别使用2种CPU内核。面向台式PC、固定式数字消费设备以及高性能服务器的处理器产品,将采用Bulldozer CPU内核;面向便携式信息终端、笔记本电脑等的处理器产品,则计划集成低功耗的Bobcat CPU内核。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。